西安交通大学微电子学院研究成果发表在“芯片奥林匹克”ISSCC 2026

日期:2026-03-11 点击数: 来源:

2月15日-2月19日,微电子学院桂小琰教授赴美国旧金山参加2026年“芯片奥林匹克”国际固态电路会议(ISSCC),并做题为“A 112-Gb/s PAM4 SBD Transceiver with Mismatch-Compensated 2xVDD Hybrid and Two-Step Echo Canceller in 28nm CMOS”的学术报告,向全球集成电路设计领域的同行展示了我校在超高速有线收发接口芯片领域的国际领先成果。

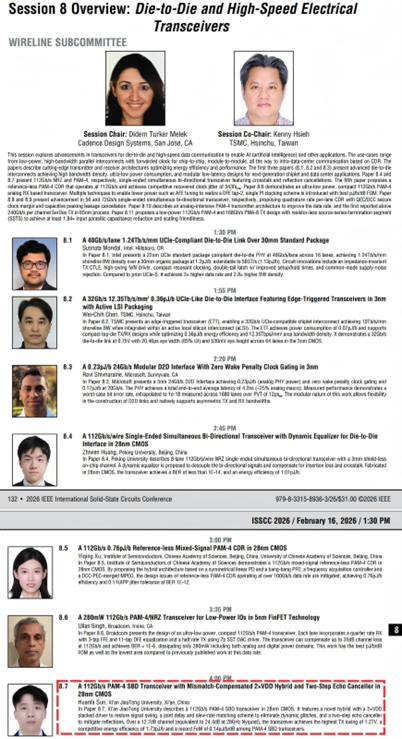

本年度高速互连接口芯片领域入选的论文中既有全球AI芯片的领跑者,英伟达(Nvidia)、博通(Broadcom)、美满(Marvell),也有传统巨头,包括Intel、台积电(TSMC)、微软等,还有加州大学伯克利分校(UC Berkeley)等高校,代表了全球最前沿和最领先的技术趋势。桂小琰教授团队全双工收发芯片研究成果也是近年来第3篇入选ISSCC(我校历史共发表ISSCC论文6篇)的超高速有线通讯接口芯片成果,标志着团队在高速有线通讯接口芯片设计领域持续保持国际一流水准。

论文展示的成果聚焦于高速有线通信收发机芯片设计,面向数据中心高带宽密度互连应用,研制了全球首款针对112-Gb/s中距离(Medium-Reach)互连传输的同时双向传输(Simultaneous Bi-Direction)收发芯片,创新性地提出了带有失配补偿的2×VDD混合电路架构(Hybrid)和两步式回波消除器(Echo Canceller)。基于28nm CMOS工艺,该芯片实现了已有单通道同时双向传输的最高数据率。对比国际上已发表的收发芯片,该成果实现了目前国际上同类型成果中1.73pJ/bit的最低功耗和0.072pJ/bit/dB的最优品质因数(FoM)。

会议期间,本成果也得到来自英伟达、博通、美满、联发科(MTK)、TSMC、Cadence等全球一流企业的研发专家的广泛关注和高度评价。

论文信息:

“A 112Gb/s PAM-4 SBD Transceiver with Mismatch-Compensated 2×VDD Hybrid and Two-Step Echo Canceller in 28nm CMOS” ,第一作者为我院博士研究生孙焕发。

本研究得到了国家自然科学基金的大力支持。

关于ISSCC

ISSCC国际固态电路会议由IEEE固态电路学会举办,是全球学术界和工业界公认的集成电路设计领域最高级别会议,被认为是集成电路设计领域的“芯片奥林匹克大会”。始于1953年的ISSCC通常是各个时期国际上最尖端固态电路技术最先发表之地,每年吸引超过3000名来自世界各地工业界和学术界的参会者。本届ISSCC收到全球共1025篇投稿论文,竞争异常激烈,最终仅有257篇论文入选,每篇论文都代表着当前芯片领域最前沿的研究成果。

【关闭】